Operating Characteristics

Pin Control for MCLR (MCLRE)

Note: These settings control the operation of the microcontroller such as various reset control

MCLRE is a single configuration bit residing in CONFIG1.

MCLRE controls the function of the MCLR /Vpp pin.

MCLRE is ignored if the Low Voltage Programming (set by the LVP configuration bit) is not enabled.

The settings for MCRLE are:

| MCLRE | Setting | Function |

|---|---|---|

| 1 | ON | Pin function is MCLR /Vpp with internal weak pull-up enabled |

| 0 | OFF | Pin function is digital input with internal pull-up controlled by WPUx |

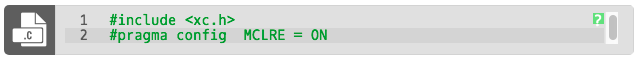

Example: Leaving MCRL/Vpp as the RESET pin.

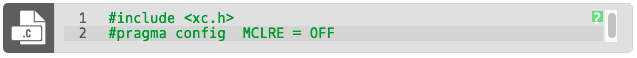

Making MCRL/Vpp a digital input pin.

Power UP Timer (PWRTE)

PWRTE is a single configuration bit residing in CONFIG2.

The Power Up Time provides a nominal 72 ms delay after a Power On Reset or a Brownout Reset to allow Vdd to stabilize. Enabling or disabling this delay is controlled by PWRTE.

The options for PWRTE are:

| PWRTE | Setting | Power-up Timer Function |

|---|---|---|

| 0 | ON | Disabled |

| 1 | OFF | Enabled |

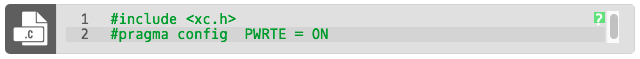

Example Enabling Power On Timer

Watchdog Timer Enable (WDTE)

The WDTE configuration setting consists of two individual bits: WDTE1 and WDTE0. The WDTE bit-field resides in CONFIG1.

WDTE allows an MCU RESET to occur if the internal Watch Dog Timer rolls over from 0xFF to 0x00 before the MCU can execute a CLRWDT instruction.

There are four options for the two WDTE bits:

- Watch Dog Timer Reset is always enabled.

- Watch Dog Timer Reset is always disabled.

- Watch Dog Timer Reset is enabled when running but disabled when MCU enters SLEEP Mode.

- Watch Dog Timer Reset is controlled at run-time by SWDTEN bit of the WDTCONregister.

| WDTE | Setting | Watch Dog Reset Function |

|---|---|---|

| 1 1 | ON | Always Enabled |

| 0 0 | OFF | Always Disabled |

| 1 0 | NSLEEP | Enabled while ACTIVE, Disabled when in SLEEP mode |

| 0 1 | SBODEN | Controlled by SBOREN bit of PCON Register |

Hardware Stack Overflow (STVREN)

STVREN is a single configuration bit residing in CONFIG2.

The STVREN configuration bit enables or disables a RESET on a stack overflow or underflow.

A stack overflow or underflow always sets the STKOVF or STKUNF bit in the PCONregister regardless of STVREN's value.

The options for STVREN are:

| STVREN | Setting | Function |

|---|---|---|

| 1 | ON | Stack over/underflow RESET is ENABLED |

| 0 | OFF | Stack over/underflow RESET is DISABLED |

The configuration bits and settings for individual PIC16F1xxx devices can be different. Check your datasheet for the specifics of the PIC MCU configuration bits you are using.

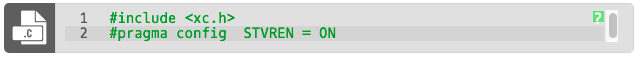

Example Enabling Stack Reset

DEBUG - Debug Mode

The DEBUG bit in Configuration Word 2 is managed automatically MPLAB X IDE.

To ensure proper device operation, this bit should not be altered!