System Clocking

Clock Source (FOSC)

FOSC consists of three individual configuration bits: FOSC2, FOSC1, and FOSC0. The FOSC bit-field is located in CONFIG1.

FOSC selects the clock source for MCU.

The FOSC Options are:

| FOSC<2:0> | Setting | Clock Soure |

|---|---|---|

| 0 0 0 | INTOSC | Internal Oscillator |

| 0 0 1 | EXTRC | External RC Oscillator |

| 0 1 0 | HS | External High Speed Crystal Oscillator |

| 0 1 1 | XT | External Crystal Oscillator |

| 1 0 0 | LP | External Low Power Crystal Oscillator |

| 1 0 1 | ECH | External Clock w/ frequency range 4 - 32 MHz |

| 1 1 0 | ECM | External Clock w/ frequency range 0.5 - 4 MHz |

| 1 1 1 | ECL | External Clock w/ frequency range 0 - 0.5 MHz |

Example: Selecting the System Clock

Fail-Safe Clock Monitor (FCMEN)

The FCMEN is a single configuration bit residing in CONFIG1.

FCMEN controls the operation of the Fail-Safe Clock Monitor allowing the clock to switch from external to internal in the event of an external clock failure.

The options for FCMEN are:

| FCMEN | Setting | Fail-Safe Clock Monitor Function |

|---|---|---|

| 0 | OFF | Disabled |

| 1 | ON | Enabled |

Example: Enabling Fail-Safe Clock Monitor

Internal/External Switch-over (IESO)

The IESO is a single configuration bit residing in CONFIG1.

IESO sets the mode for clock switching and two-speed start-up. With IESO enabled the clock source can be controlled by the application program.

The options for IESO are:

| IESO | Setting | Two Speed Star-up Function |

|---|---|---|

| 0 | OFF | Disabled |

| 1 | ON | Enabled |

Example: Enabling Two Speed Start-up

Enabling Clock Output (CLKOUTEN)

The CLKOUTEN is a single configuration bit residing in CONFIG1.

CLKOUTEN allows the OSCx/CLCKOUT pin to output the internal system clock. This allows the PIC16F1xxx system clock to drive other components.

The options for CLKOUTEN are:

| CLKOUTEN | Setting | CLKOUT function |

|---|---|---|

| 0 | ON | Fosc will be output to OSCx/CLKOUT |

| 1 | OFF | OSCx/CLKOUT will be the oscillator or a peripheral function |

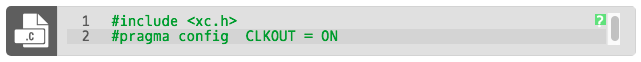

Example: Outputing the Internal System Clock

Phase Lock Loop Enable (PLLEN)

PLLEN is a single configuration bit residing in CONFIG2.

The internal oscillator's 4 X Phase Lock Loop( PLL) is controlled by a combination of the PLLEN configuration bit and the SPLLEN bit in the OSCON register.

The options for PLLEN are:

| PLLEN | Setting | Internal PLL function |

|---|---|---|

| 0 | ON | 4 X PLL is always enabled |

| 1 | OFF | 4 X PLL is controlled by SPLLEN bit in OSCCON |

Not all PIC16F1xxx MCUs have the same options for the PLL. Please refer to the datasheet of the PIC MCU you are using to determine the specific PLL configuration settings.

Example: Enabling the Internal Phase Lock Loop