Device Security

CPD - Data EEPROM Read Protection

CPD is a single configuration bit residing in CONFIG1.

The internal data EEPROM memory can be protected from external reads with CPD. External programmers are prohibited from reading protected EEPROM. The contents of EEPROM is still available for reads from internal sources.

The settings for CPD are:

| CPD | Setting | EEPROM Read Protection Function |

|---|---|---|

| 0 | ON | Enabled - EEPROM is not readable |

| 1 | OFF | Disabled - EEPROM is readable |

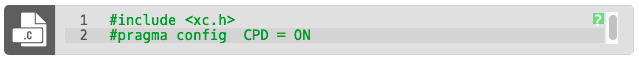

Example: Disabling EEPROM Reads from External Sources

Program Memory READ protection (CP)

CP is a single configuration bit residing in CONFIG1.

The entire program memory space can be protected from external reads with CP.

You will see all '0's when you read protected program memory. The contents of program memory are still available for reads from internal sources.

The settings for CP are:

| CP | Setting | Read Protection Function |

|---|---|---|

| 0 | ON | Enabled - memory is not readable |

| 1 | OFF | Disabled - memory is readable |

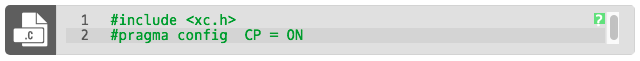

Example: Disabling External Program Memory Reads

Flash Self Write Enable (WRT)

WRT consists of two individual configuration bits: WRT1 and WRT0. The WRT bit-field is located in CONFIG2.

WRT establishes the address range in which the Program Memory can be written by the user program.

The settings for WRT are:

| WRT | Setting | Flash Self Right Functionality |

|---|---|---|

| 1 1 | ALL | No memory can be written to by user program |

| 1 0 | BOOT | Address range 0 - 0x1FF write protected 200h - FFFn write-able |

| 0 1 | HALF | Address range 0 - 0x7FF write protected 800h - FFFn write-able |

| 0 0 | OFF | All memory addresses can be written to by user program |

Not all PIC16F1xxx MCUs have the same WRT options as shown. Please refer to the datasheet of the PIC MCU you are using to determine the WRT options for the device you are using.