Indirect Addressing

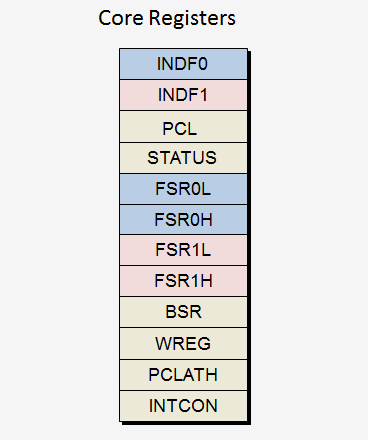

Enhanced Mid-Range PIC MCUs have two channels that indirectly access data memory. Each channel uses three core registers to implement indirect addressing.

FSR0L, FSR0H, and INDF0 control channel 0

FSR1L, FSR1H, and INDF1 control channel 1

Register Usage

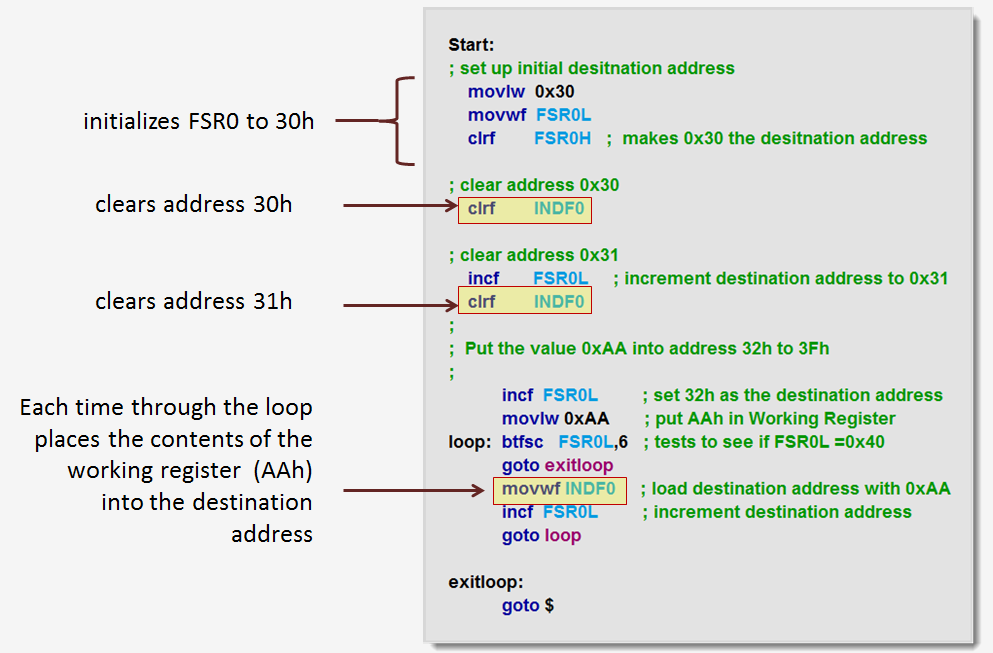

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR1H/FSR1L or FSR0H/FSR0L)

To access an address indirectly: first, write the address into FSRn, then execute an instruction with INDFn as the operand.

Sample Code using Indirect Addressing

Indirect Addressing Modes

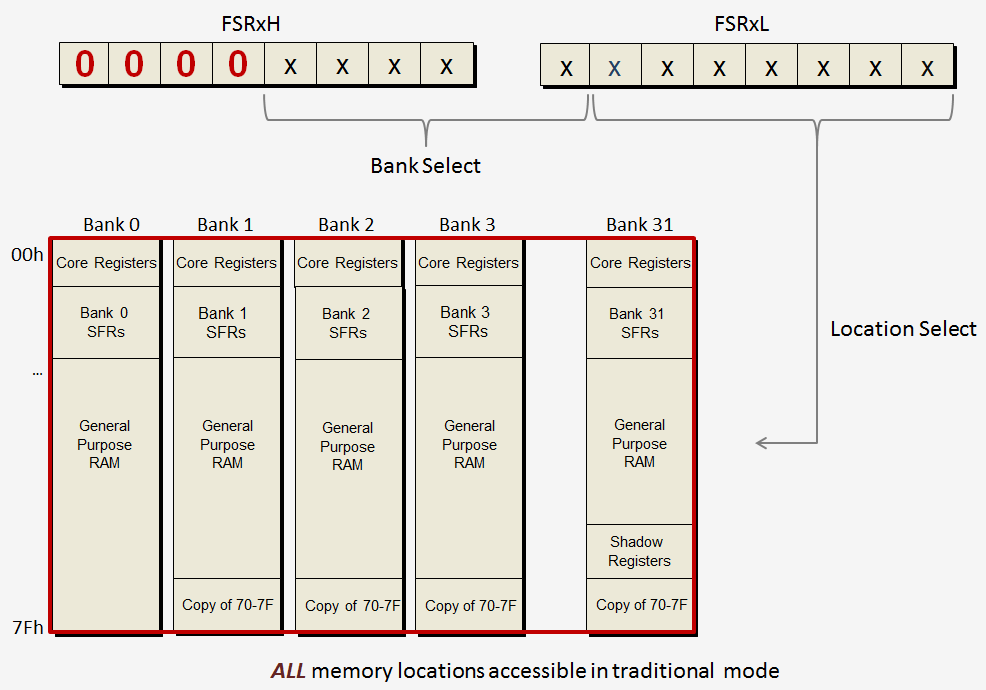

The FSR registers form a 16-bit address that allows an address space with 65536 possible values. Depending on the value placed in FSRn registers, a PIC16F1xxx MCU will access the memory in one of three different modes:

Traditional Data Memory Access

When the value of FSRn is between 0h and FFFh instructions using INDFn will access the memory in the Traditional Access Method. In this mode of operation, all memory locations including Special Function Registers, General Purpose RAM, and the Common memory are accessible through INDFn.

Linear Data Memory Access

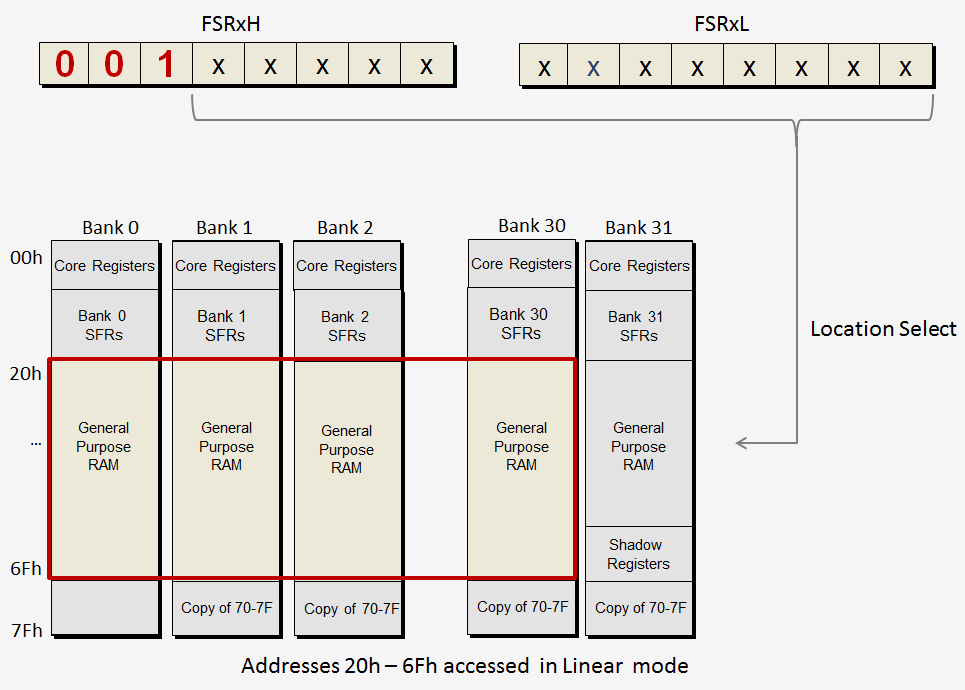

Each memory bank contains 80 bytes of general purpose memory (addresses 20h-6Fh). When the application requires an array or buffer of data which exceeds 80 bytes, traditional indirect access may not provide a convenient interface to the data structure. The linear addressing method is designed to handle data structures larger than 80 bytes.

When FSRxH<7:5> contains '001' the general-purpose sections of the data banks are accessed as if they were one contiguous memory block. When an FSR is incremented beyond the GPR limit of a bank, the GPR memory of the next bank is automatically accessed making the entire GPR memory appear as one contiguous block.

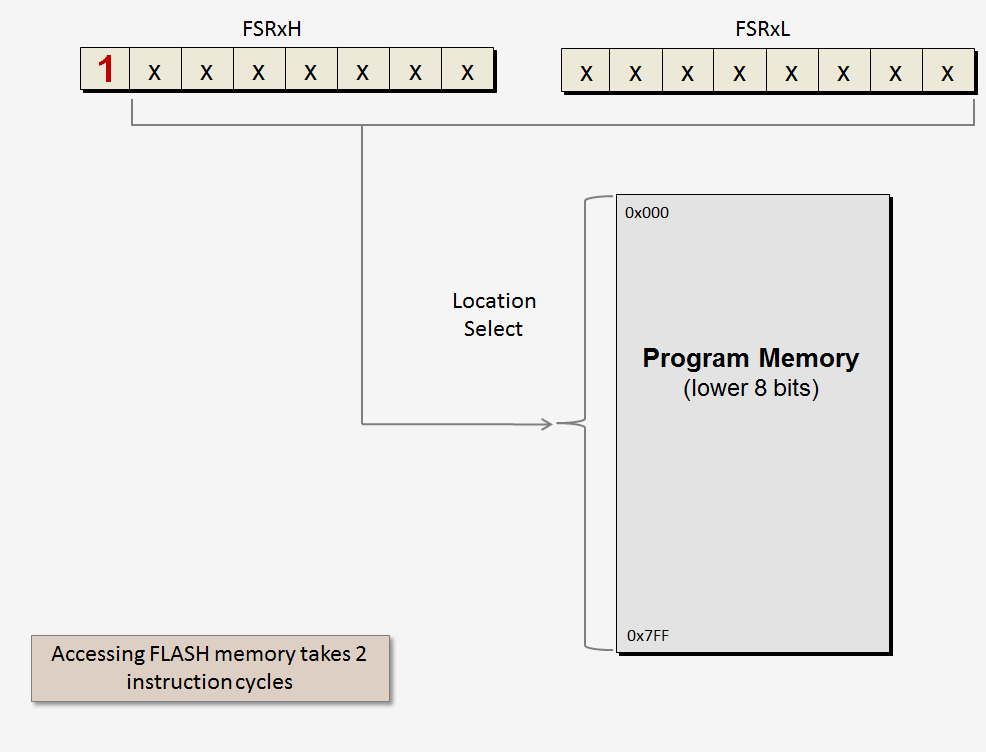

Program Memory (FLASH) Access

To make constant data access easier, the entire program Flash memory can be mapped to the FSR space. When Bit7 of the FSRxH register is set, the remaining 15 bits of FSR point to an address in Program memory. In the Program Memory mode, the MCU's flash memory contents can be read, but not altered. When accessed, only the lower 8 bits of the program memory is read. Access to an unimplemented memory address will always return a '0'.