Overview

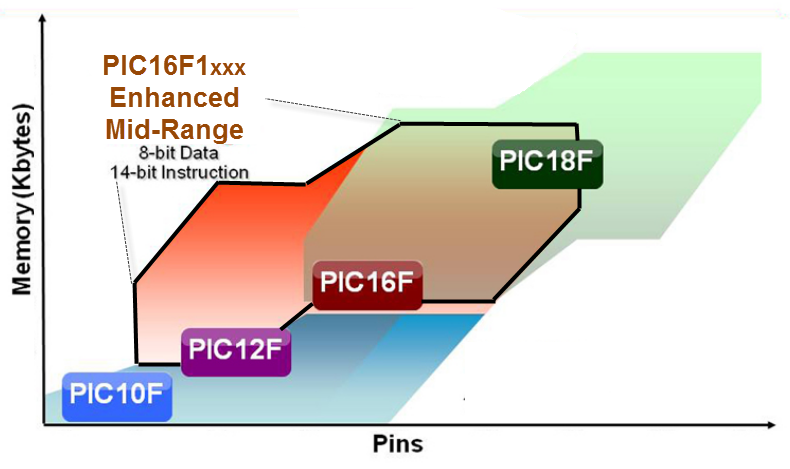

Microchip 8-bit MCU Families

The PIC16F1xxx Enhanced Mid-Range 8-bit PIC®MCU Family spans a wide array of memory sizes and I/O pins.

This page presents the key architectural features of the PIC16F1xxx family of MCUs. Links are provided in this page to the technical details needed to implement applications on the enhanced mid-range PIC MCU family.

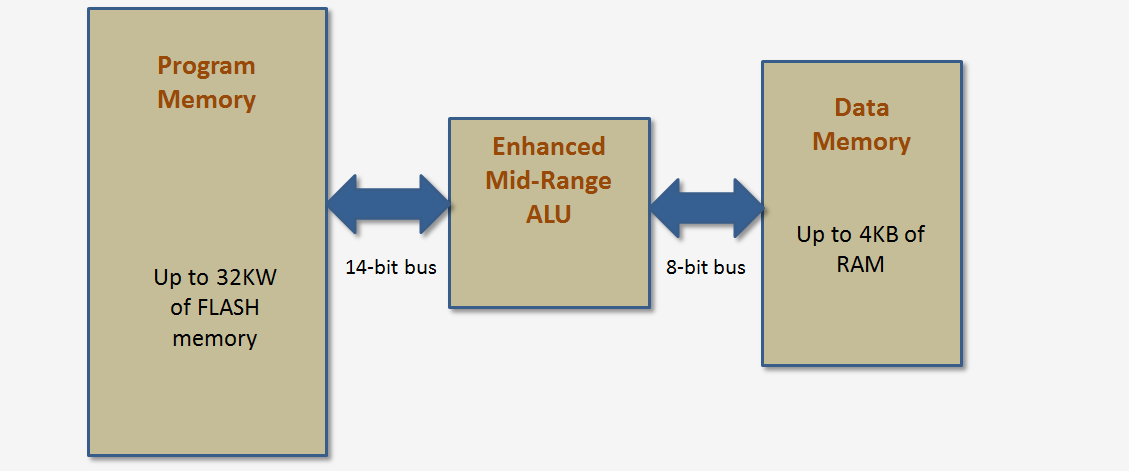

Harvard Architecture

Enhanced mid-range PIC® MCUs use a dual-bus Harvard Architecture.

Instruction Bus

Program instructions are fed into the ALU from FLASH program memory via the 14-bit instruction bus. On every instruction clock cycle, one 14-bit program word is read into the ALU.

Data Bus

An 8-bit data bus connects the ALU to the Data Memory space. During each instruction the ALU can read data from data memory location, modify the data, then write the data back to memory.

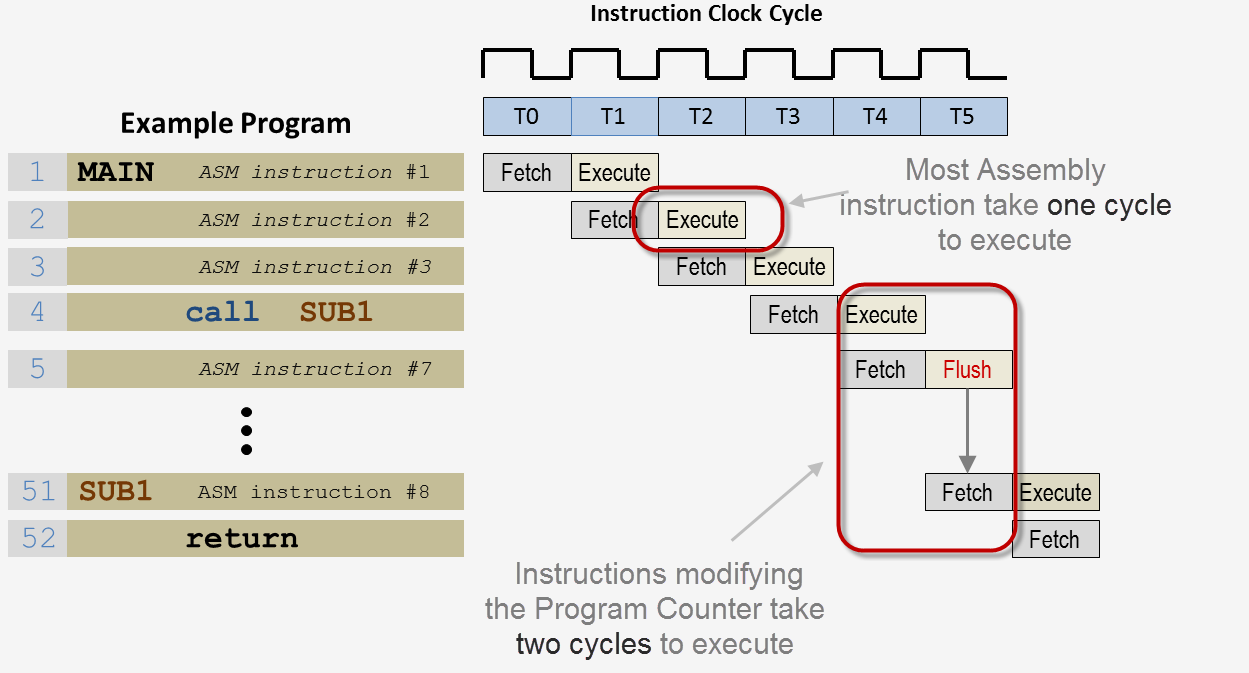

Instruction Pipelining

The enhanced mid-range PIC's dual-bus architecture provides for a two-stage instruction pipeline. Once each clock cycle, two instruction phases execute:

- The next instruction is "fetched" from Program Memory

- The current instruction is "executed" and reads/modifies/writes data memory (if needed)