Registers used to Process Interrupts

Interrupt Control Register

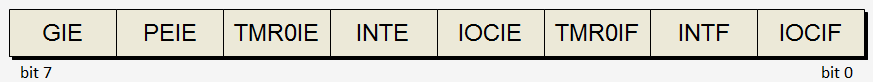

INTCON Register

- GIE: Global Interrupt Enable

- PEIE: Peripheral Interrupt Enable

- TMR0IE: Timer0 Interrupt Enable

- INTE: External Interrupt Enable

- IOCIE: Interrupt on Change Enable

- TMR0IF: Timer0 Interrupt flag

- INTF: External Interrupt flag

- IOCIF: Interrupt on Change flag

INTCON contains global and peripheral interrupt enable flags as well as the individual interrupt request flags and interrupt enable flags for three of the PIC16F1xxxx interrupts.

Interrupt Enable Registers

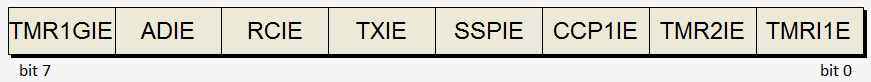

PIE1 Register

- TMR1GIE: Timer1 Gate Interrupt Enable

- ADIE: Analog-to-Digital Converter Interrupt Enable

- RCIE: USART Receive Interrupt Enable

- TXIE: USART Transmit Interrupt Enable

- SSPIE: Synchronous Serial Port (MSSP) Interrupt Enable

- CCP1IE: CCP1 Interrupt Enable

- TMR2IE: Timer2 Interrupt Enable

- TMR1IE: Timer1 Interrupt Enable

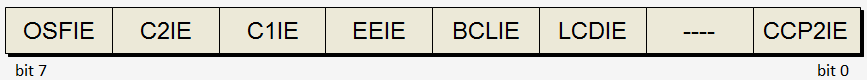

PIE2 Register

- OSFIE: Oscillator Fail Interrupt Enable

- C2IE: Comparator C2 Interrupt Enable

- C1IE: Comparator C1 Interrupt Enable

- EEIE: EEPROM Write Completion Interrupt Enable

- BCLIE: MSSP Bus Collision Interrupt Enable

- LCDIE: LCD Module Interrupt Enable

- --- : Unimplemented, read as '0'

- CCP2IE: CCP2 Interrupt Enable

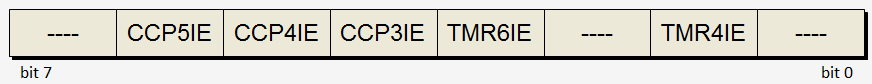

PIE3 Register

- --- : Unimplemented read as '0'

- CCP5IE: CCP5 Interrupt Enable

- CCP4IE: CCP4 Interrupt Enable

- CCP3IE: CCP3 Interrupt Enable

- TMR6IE: Timer6 Interrupt Enable

- --- : Unimplemented, read as '0'

- TMR4IE: Timer4 Interrupt Enable

- --- : Unimplemented, read as '0'

PIE1, PIE2, and PIE3 contain the individual interrupt enable flags for the MCU's peripherals.

Interrupt Request Registers

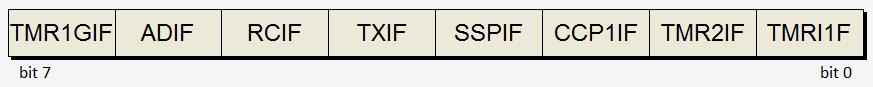

PIR1 Register

- TMR1GIF: Timer1 Gate Interrupt Flag

- ADIF: Analog-to-Digital Converter Interrupt Flag

- RCIF: USART Receive Interrupt Flag

- TXIF: USART Transmit Interrupt Flag

- SSPIF: Synchronous Serial Port (MSSP) Interrupt Flag

- CCP1IF: CCP1 Interrupt Flag

- TMR2IF: Timer2 Interrupt Flag

- TMR1IF: Timer1 Interrupt Flag

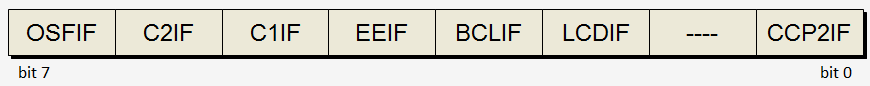

PIR2 Register

- OSFIF: Oscillator Fail Interrupt Flag

- C2IF: Comparator C2 Interrupt Flag

- C1IF: Comparator C1 Interrupt Flag

- EEIF: EEPROM Write Completion Interrupt Flag

- BCLIF: MSSP Bus Collision Interrupt Flag

- LCDIF: LCD Module Interrupt Flag

- --- : Unimplemented, read as '0'

- CCP2IF: CCP2 Interrupt Flag

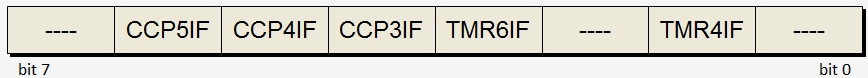

PIR3 Register

- --- : Unimplemented, read as '0'

- CCP5IF: CCP5 Interrupt Flag

- CCP4IF: CCP4 Interrupt Flag

- CCP3IF: CCP3 Interrupt Flag

- TMR6IF: Timer6 Interrupt Flag

- --- : Unimplemented, read as '0'

- TMR4IF: Timer4 Interrupt Flag

- --- : Unimplemented, read as '0'

PIR1, PIR2, and PIR3 contain the individual interrupt request flags for the MCU's peripherals

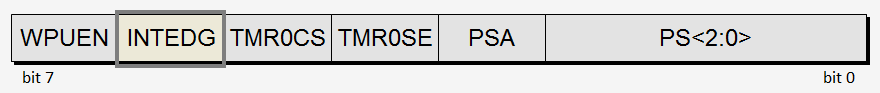

OPTION_REG

OPTION_REG

The INTEDG flag in OPTION_REG is used to set a rising or failing edge on the INT pin as the trigger for an INTE interrupt.