Shadow Registers

The PIC32 processor implements one or more copies of the General Purpose Registers (GPR) for use by high-priority interrupts. The extra banks of registers are known as Shadow Register Sets. When a high-priority interrupt occurs, the processor automatically switches to a shadow register set without software intervention. This reduces overhead in the interrupt handler and reduces effective latency.

The shadow register sets are controlled by registers located in the System Coprocessor (CP0) as well as the interrupt controller hardware located outside of the CPU core.

PIC32MZ application software is responsible for enabling the use of shadow register sets via the appropriate definition of the ISR handler function, as well as initialization of the PRISS register, as described here.

PIC32MZ2048EFG100 implements seven shadow register sets. Please refer to the device data sheet for information as to how many shadow register sets are available in your device.

Basic Operation

An interrupt exception request is decoded by the interrupt controller. The vector number, requested priority level and shadow register set numbers are provided to the CPU core as shown:

The shadow register set number is then written to the SRSCtlEICSS bit-field, which is used to select the "current shadow set" for the interrupt.

The microAptiv/M5150 core then uses this information to perform the following:

- The current GPR Bank ID is copied into the SRSCtlPSS field of the SRSCtl register. This is the Previous Shadow Set (PSS) ID to be recovered later when the interrupt exception request is completed.

- The GPR set ID pulled from SRSCtlEICSS is copied into the SRSCtlCSS field of the SRSCtl register. This now specifies the Current Shadow Set (CSS).

- Execution of the interrupt exception handler proceeds to completion, and an IRET instruction is executed.

- The core then copies the values from the SRSCtlPSS bit field into the SRSCtlCSS bit field and execution resumes from the point at which the interrupt exception was issued.

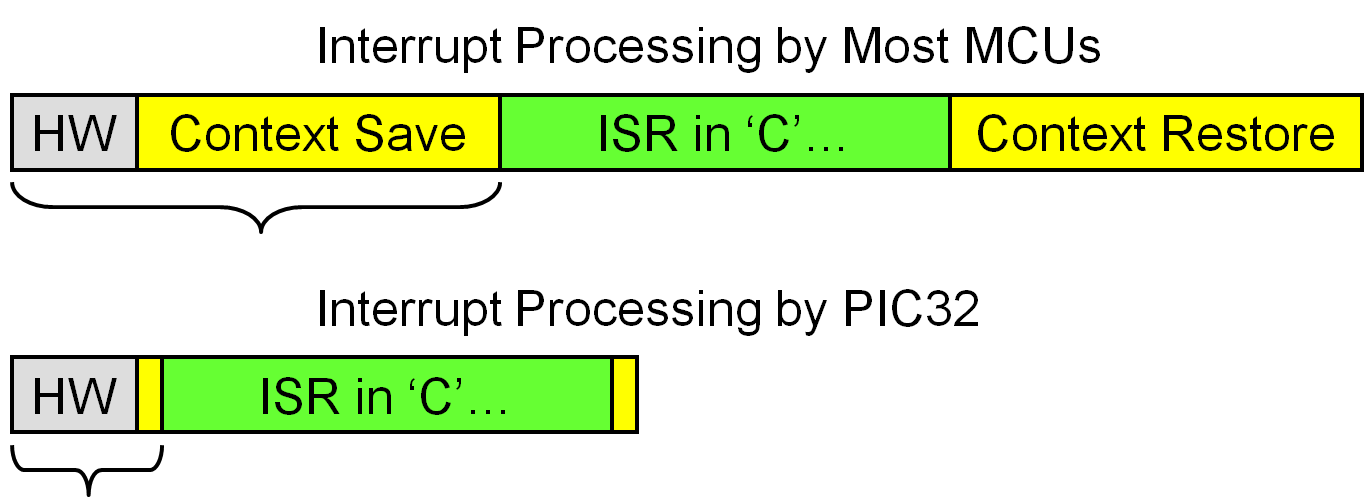

Interrupt Automated Prologue/Epilogue (IAP/IEP)

In addition to the use of the Shadow Register Sets to reduce latency, the PIC32MZ core implements the MIPS MCU ASE feature-set, which defines these additional latency-saving mechanisms.

Interrupt Automated Prologue (IAP)

The MCU ASE adds additional hardware logic that automatically saves some of the CP0 register states in the stack and automatically updates some of the CP0 registers in preparation for interrupt handling.

Interrupt Automated Epilogue (IAE)

A mirror to the Automated Prologue, this feature automates the restoration of some of the CP0 registers from the stack and the preparation of some of the CP0 registers for returning to non-exception mode. This feature is implemented within the IRET instruction, which is introduced in this ASE.