Results

Part 1. Error 1 (Illegal Address Exception - main.c - line 145 executed)

LED LD6 will light up to indicate the occurrence of this exception:

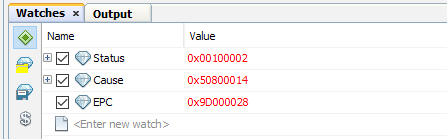

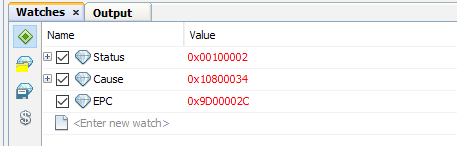

In MPLAB® X, open the Watches Window window and add the Status, Cause, and EPC CP0 registers to the view:

The Status register reads 0x00100002. Ignore the leading 0x0010 for now and focus on the last nibble 0x2 (StatusEXL = 1). Per the PIC32 Datasheet, this indicates that there is an error.

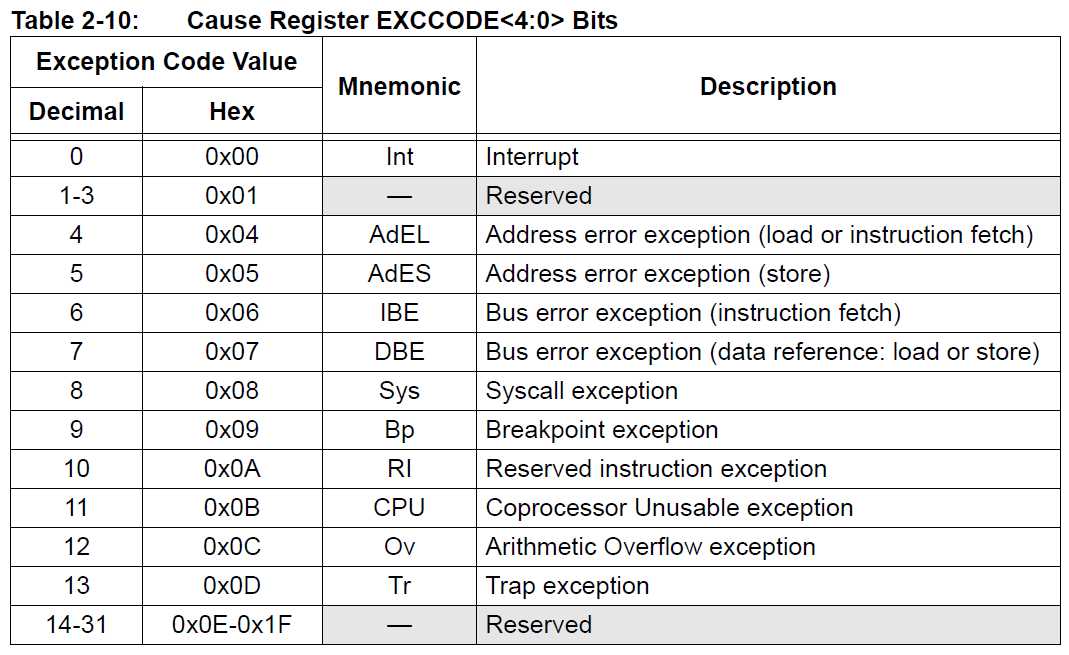

The Cause register reads 0x50800014. Ignore the leading 0x5080 for now. The LSB value of 0x14 is tricky since it is not properly aligned within the LSB to directly represent the EXCCODE value. We need to convert this number to the true value of the structure within CauseEXCCODE. Right shift 0x14 twice, and we get the value 0x05. Looking at the exception cause table in the PIC32MX CPU Family Reference Manual, we see that this equates to ADDRESS ERROR EXCEPTION (STORE):

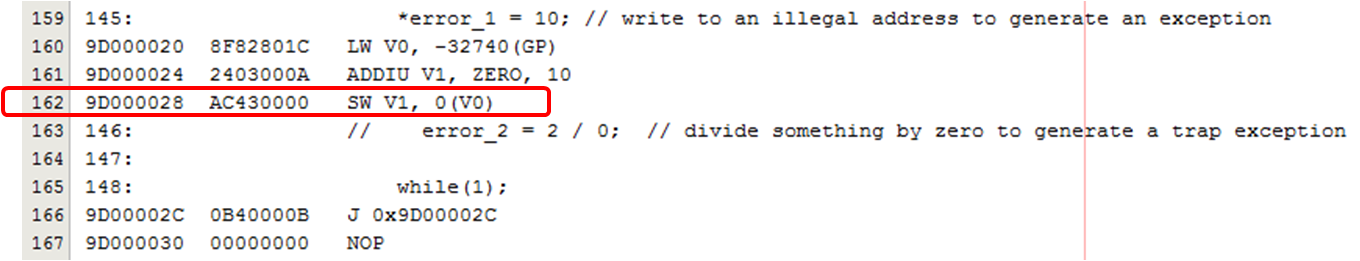

The EPC register reads 0x9D000028. This is the address of the instruction which the CPU will resume processing after returning from exception. We can confirm this by displaying the disassembly listing file.

In MPLAB X, select Window-->Debugging-->Output-->Disassembly Listing File:

This is an example of a precise exception, whereby the EPC value identifies the instruction that caused the exception.

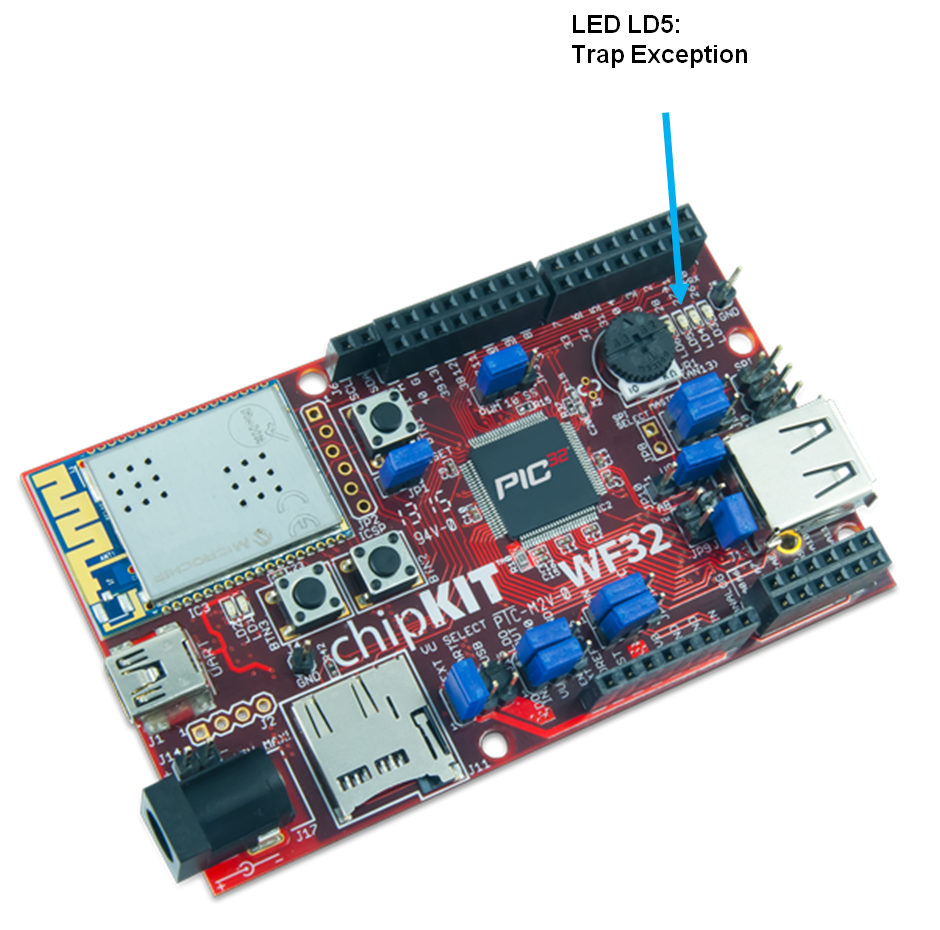

Part 2. Error 2 (Trap Exception - main.c - line 146 executed)

LED LD5 will light up to indicate the occurrence of this exception:

In MPLAB® X, open the Watches Window window and add the Status, Cause, and EPC CP0 registers to the view:

The Status register reads 0x00100002. Ignore the leading 0x0010 for now and focus on the last nibble 0x2 (StatusEXL = 1). Per the PIC32 Datasheet, this indicates that there is an error.

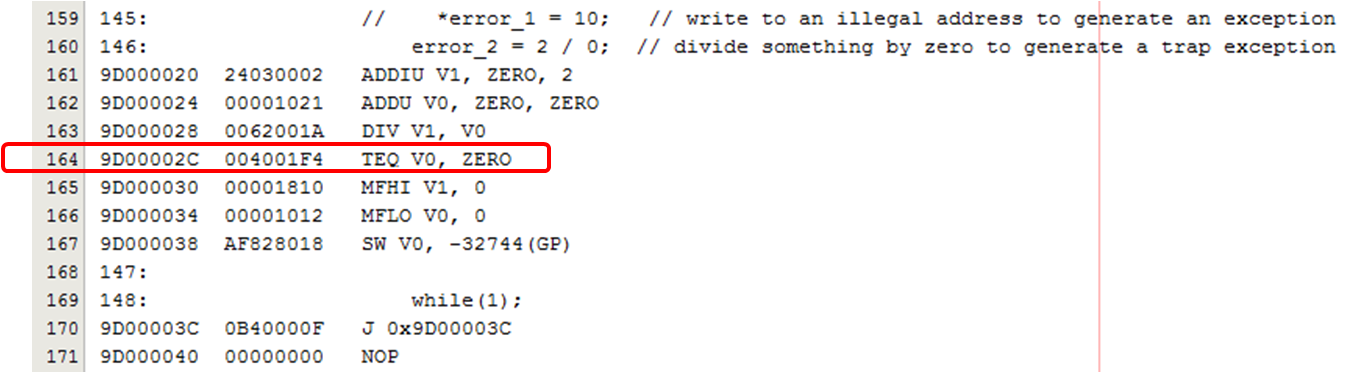

The Cause register reads 0x10800034. Right shift the LSB 0x34 twice, and we get the value 0x0D. Looking at the exception cause table in the PIC32MX CPU Family Reference Manual (shown above), we see that this equates to a TRAP EXCEPTION.

The EPC register reads 0x9D00002C. This is the address of the instruction which the CPU will resume processing after returning from exception.

In MPLAB X, select Window-->Debugging-->Output-->Disassembly Listing File:

This is an example of an imprecise exception, whereby the EPC value does not identify the instruction that caused the exception. In this example, the divide operation is carried out by the Multiply-Divide Unit which runs in parallel to the main CPU. The EPC value points to the CPU instruction that was interrupted by the MDU exception.