Instruction Categories

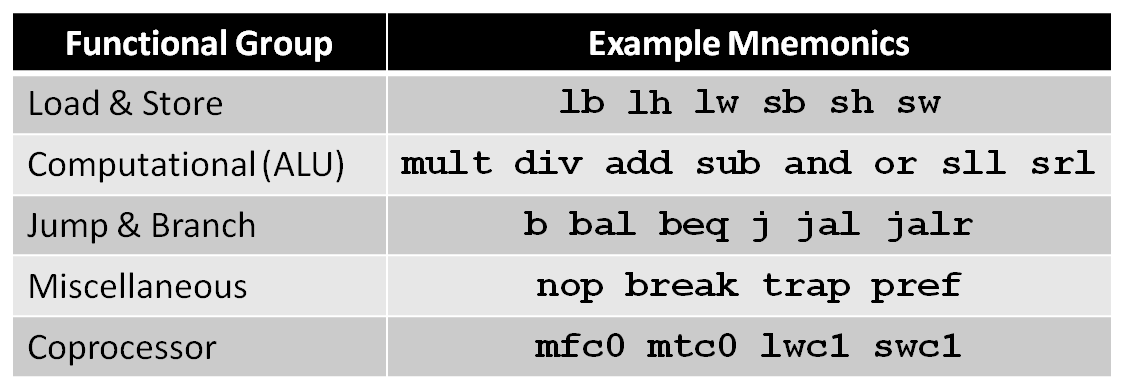

MIPS32 Release 2 Central Processing Unit (CPU) instructions are organized into the following functional groups:

- Load and Store: Used to load/store operands from memory to/from the General Purpose Register (GPR)

- Computational: Arithmetic, Logic and Shift operations performed on integers represented in two's complement format

- Jump and Branch: Instructions that modify the Program Counter (PC)

- Miscellaneous: Exception handling, conditional move, Cache Prefetch, NOP

- Coprocessor: Instructions that deal with the coprocessor units

The following table provides some example assembly language mnemonics for these categories:

MIPS32 Release 2 CPU Instructions are fully documented in MIPS® Architecture For Programmers Volume II-A: The MIPS32® Instruction Set.

Macro Instructions

Most MIPS assemblers will synthesize a set of macro (also called synthetic or pseudo) instructions intended to simplify the task of writing MIPS assembly language programs.

Every time a programmer specifies a macro instruction, the assembler replaces it with a set of actual MIPS instructions to accomplish a task.

For example, let us suppose a programmer used the load-immediate (li) macro instruction to load a 32-bit constant into a register:

li s0, 0x1234AA77

The MIPS assembler would then insert the following two MIPS instructions to accomplish the task:

lui s0, 0x1234 ori s0, 0xAA77Some pseudo-instructions require a temporary register for intermediate calculations. Assemblers use register at for this purpose.

The mere existence of "macro" assembly instructions should be a warning sign to budding MIPS assembly language programmers - MIPS machine code might be rather dreary to write!

This article provides a list of commonly synthesized pseudo-instructions.